Analog Devices Inc. Récepteur et émetteur RF direct 4T4R AD9988

Le récepteur et émetteur RF direct 4T4R AD9988 d'Analog Devices Inc. est un composant hautement intégré avec quatre cœurs de convertisseur numérique-analogique (CNA) à fréquence d'échantillonnage maximale de 12 GS/s et quatre cœurs de convertisseur analogique-numérique (CAN) RF de 12 bits et 4 GS/s. L'AD9988 prend en charge quatre canaux émetteurs et quatre canaux récepteurs avec une configuration 4T4R.Le récepteur et émetteur RF Direct 4T4R AD9988 d'ADI est conçu pour les applications d'émetteur TDD à quatre antennes, où le chemin du récepteur est partagé entre les modes récepteur et d'observation. La cohérence de phase est maintenue tandis que les broches GPIO peuvent être configurées et déclenchées pour prendre en charge différents modes utilisateur. Le composant offre une bande passante de canal radio maximale de 1,2 GHz dans une configuration 4T4R et une résolution d'échantillonnage de 16 bits.

L'AD9988 dispose d'un port de données série JESD204C 16 voies 24,75 Gbit/s ou JESD204B 15,5 Gbit/s qui permet jusqu'à huit voies par liaison émission/réception, un multiplicateur d'horloge sur puce et une capacité de traitement du signal numérique ciblant plusieurs bandes directement vers les applications radio RF.

Caractéristiques

- Conception d'une plateforme radio commune flexible et reconfigurable

- Largeur de bande des canaux de l'émetteur/récepteur jusqu'à 1,2 GHz (4T4R)

- Plage de fréquences RF RF DAC/RF ADC jusqu'à 7,5 GHz

- PLL sur puce avec synchronisation multi-puces

- Option d'entrée d'horloge RF externe

- Caractéristiques numériques polyvalentes

- Filtres d'interpolation et de décimation sélectionnables

- DDC et DUC configurables

- 8 DUC complexes fins (FDUC) et 4 DUC complexes grossiers (CDUC)

- 8 DDC complexes fins (FDDC) et 4 DDC complexes grossiers (CDDC)

- Les FDUC et les FDDC sont entièrement contournables

- 2 NCO 48 bits indépendants par DUC ou DDC

- Filtre PFIR 192-tap programmable pour égalisation de réception

- Prend en charge 4 paramètres de profil différents chargés via GPIO

- Recevoir le support AGC

- Détection rapide avec faible latence pour un contrôle AGC rapide

- Surveillance de signal pour contrôle AGC lent

- Broches de support AGC dédiées

- Prise en charge DPD de transmission

- Délai et gain programmables par chemin de transmission de données

- Ajustement de délai DDC grossier pour le chemin d'observation DPD

- Prise en charge de données numériques réelles ou complexes (8, 12 ou 16 bits)

- Caractéristiques auxiliaires

- Pilote d'horloge CAN avec rapports de division sélectionnables

- Circuit de protection en aval de l'amplificateur de puissance

- Unité de surveillance de la température sur puce

- Les broches GPIO programmables prennent en charge le basculement entre les modes

- Option d'économie d'énergie TDD et CAN de partage

- Interface SERDES JESD204B ou JESD204C, 16 voies jusqu'à 24,75 Gbit/s

- Émetteur JESD204B/C 8 voies (JTx) et récepteur JESD204B/C 8 voies (JRx)

- Prise en charge de la sous-classe 1

- Prend en charge la synchronisation multi-appareils

- BGA 15 mm x 15 mm, 324 billes avec un pas de 0,8 mm

Applications

- Infrastructure de communication sans fil

- W-CDMA, LTE, LTE-A, entrée multiple et sortie multiple massive (MIMO)

- Micro-ondes point à point, bande E et onde millimétrique 5G

- Systèmes de communication large bande

- Système de terminaison de modem câble DOCSIS 3.0+ (CMTS)

- Systèmes de test et de mesure des communications

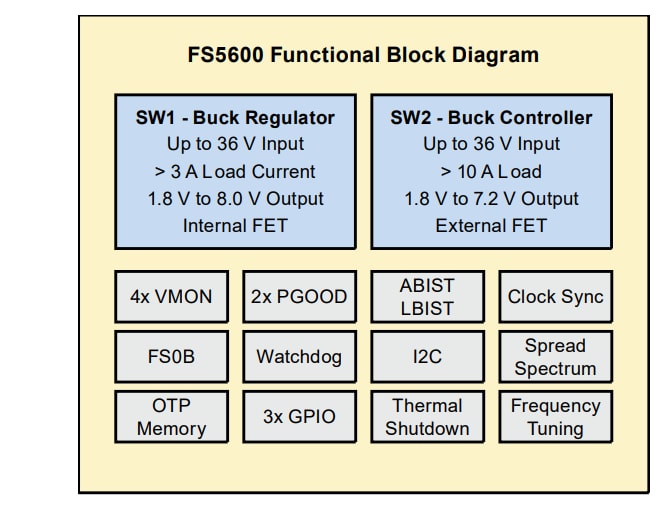

SCHÉMA DE PRINCIPE FONCTIONNEL