Lattice Semiconductor FPGA Certus™-NX

Les FPGA Cerus™-NX de Lattice Semiconductor fournissent jusqu’à deux fois la densité d’E/S par mm2 par rapport aux FPGA concurrents similaires. Les FPGA Certus-NX offrent les meilleures économies d’énergie de leur catégorie, une petite taille, une fiabilité, des performances instantanées et prennent en charge des interfaces PCI Express (PCIe) et Gigabit Ethernet rapides pour permettre le co-traitement des données, le pontage de signal et le contrôle du système. Les FPGA sont élaborés sur la plateforme FPGA Lattice Nexus™ en utilisant la technologie FD-SOI 28 nm à faible consommation. Ces composants combinent la flexibilité extrême d'un FPGA avec la faible puissance et la haute fiabilité (grâce à un niveau de SER extrêmement faible) de la technologie FD-SOI. La famille Certus-NX de FPGA à usage général à faible puissance peut être utilisée dans un large éventail d’applications sur de nombreux marchés et optimisée pour les besoins de pont et de traitement dans les applications en périphérie.Les FPGA Certus-NX de Lattice prennent en charge une variété d’interfaces, notamment PCI Express (Gen1, Gen2), SGMII (Gigabit Ethernet), LVDS, LVCMOS (0,9 V-3,3 V). Les caractéristiques de traitement sur les dispositifs comprennent jusqu'à 39 K cellules logiques, 56 multiplicateurs de 18 × 18, 2,9 Mo de mémoire intégrée (composée de blocs EBR et LRAM), une mémoire distribuée, des interfaces DRAM (avec prise en charge DDR3, DDR3L, LPDDR2 et LPDDR3 jusqu'à 1 066 Mbit/s × 16). Les FPGA disposent d'une configuration rapide de leur tissu logique reconfigurable basé sur SRAM et d'une configuration ultra-rapide (en moins de 3 ms) de leur sysI/O™ programmable. En plus de la haute fiabilité inhérente à la technologie FD-SOI (en raison de son niveau de SER extrêmement faible), les caractéristiques de fiabilité opérationnelle telles que les fonctions SED/SEC intégrées basées sur trame (pour le tissu logique de type SRAM) et ECC (pour EBR et LRAM) sont également prises en charge. Des doubles CAN 12 bits sont disponibles sur puce pour les fonctions de surveillance du système.

De nombreux modules IP (propriété intellectuelle) préconfigurés sont disponibles pour la gamme Certus-NX. En utilisant ces noyaux IP flexibles configurables sous forme de blocs normalisés, les utilisateurs sont libres de se concentrer sur les aspects uniques d'une conception, en augmentant ainsi leur productivité.

Caractéristiques

- Encombrement 3 fois plus réduit avec prise en charge PCIe et GigE, soit le boîtier le plus petit pour chaque densité, avec 6 x 6 mm, par rapport aux FPGA concurrents similaires

- Permet la mise en œuvre PCIe et GigE dans un encombrement réduit (6 mm x 6 mm)

- 2 fois plus d’E/S par mm2 avec le plus grand nombre d’E/S par boîtier, avec jusqu’à 2 fois plus d’E/S par mm2 que la concurrence

- Interfaces haut débit avec des entrées/sorties différentielles jusqu’à 70 % plus rapides (par rapport aux FPGA similaires) à 1,5 Gb/s, PCIe de 5 Gb/s, SGMII (GigE) de 1,25 Gb/s et 1 066 Mb/s

- Interfaces mémoire DDR3 également prises en charge

- Sécurité de conception : authentification de flux binaire ECDSA associée à un puissant chiffrement AES-256

- La plateforme Nexus Lattice consomme jusqu'à 4 fois moins d'énergie que les FPGA similaires

- Fiabilité 100 fois plus élevée, grâce à un taux d'erreur progressive (SER) 100 fois réduit via la technologie FD-SOI 28 nm

- La configuration d'E/S instantanée s'effectue en 3 ms et le périphérique complet en à peine 8 ms

Applications

- Passerelle PCIe/SGMII

- Co-traitement

Ressources supplémentaires

Comparaison de produits

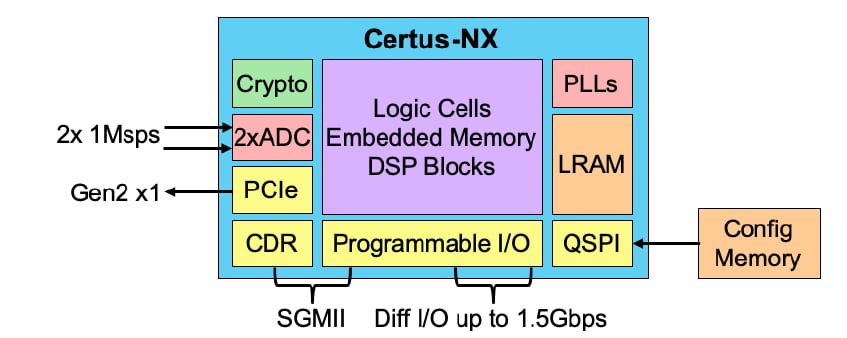

Schéma fonctionnel

Schéma PFU