Analog Devices / Maxim Integrated Authetificateurs I2C automobiles DS28C40 DeepCover

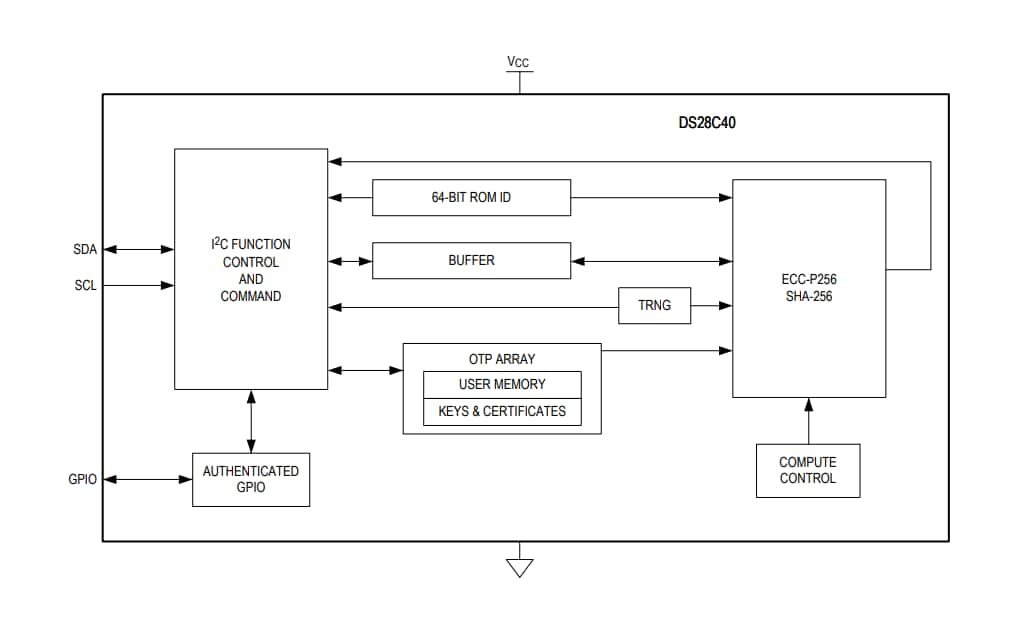

Les authentificateurs I2C automobiles DeepCover DS28C40 d'Analog Devices fournissent un ensemble d’outils cryptographiques dérivés des fonctions de sécurité asymétriques (ECC-P256) et symétriques (SHA-256) intégrées. Ces composants intègrent un véritable générateur de nombres aléatoires (TRNG) FIPS/NIST, 6 ko de mémoire OTP (mémoire morte programmable) pour les données utilisateur, les clés et les certificats, un GPIO configurable et un numéro d’identification ROM (ROM ID) 64 bits unique. Les capacités de clé publique/privée ECC sont basées sur la courbe P-256 définie par le NIST, y compris la génération et la vérification de signature ECDSA conforme FIPS 186-4 pour prendre en charge un modèle d’authentification de clé asymétrique bidirectionnel. Les capacités de clé secrète SHA-256 sont conformes à FIPS 180 et permettent de la flexibilité lorsqu’elles sont utilisées en conjonction avec les opérations ECDSA ou indépendamment pour plusieurs fonctions HMAC.La broche GPIO de l'authentificateur automobile I2C DeepCover DS28C40 d’Analog Devices peut fonctionner sous contrôle-commande et peut être configurée pour prendre en charge le fonctionnement authentifié et non authentifié. Cela inclut un mode crypto-robuste basé sur ECDSA pour prendre en charge le démarrage sécurisé d’un processeur hôte. Les solutions de sécurité intégrées DeepCover® masquent les données sensibles sous plusieurs couches de sécurité avancée, offrant un stockage de clé le plus sécurisé possible. Des contre-mesures invasives et non invasives, y compris le blindage actif de la puce, le stockage crypté des clés et les méthodes algorithmiques, sont mises en œuvre pour protéger contre les attaques de sécurité au niveau du dispositif.

Caractéristiques

- Moteur de calcul ECC-P256

- Génération et vérification de signature FIPS 186 ECDSA P256

- Échange de clés ECDH pour l’établissement de clés de session

- R/W authentifié ECDSA de mémoire configurable

- Moteur de calcul SHA-256

- FIPS 198 HMAC pour authentification bidirectionnelle

- R/W chiffré à pastille unique SHA-256 de mémoire configurable à l’aide d’une clé ECDH établie

- Une broche GPIO avec contrôle d’authentification optionnel

- Drain ouvert, 4 mA/0,4 V

- Marche/arrêt et lecture de l’état authentifiés par SHA-256 ou ECDSA en option

- Vérification du certificat ECDSA en option aux fins de définir la marche/arrêt après le hachage multibloc du démarrage sécurisé

- TRNG avec source d’entropie conforme à la norme NIST SP 800-90B avec fonction de lecture.

- Paires de clés privées/publiques (Pr/Pu) générées par puce optionnelles pour les opérations ECC

- 6 Ko de mémoire morte programmable (OTP) pour les données utilisateur, les clés et les certificats

- Numéro d’identification à 64 bits unique programmé en usine (ID ROM)

- Composant de données d’entrée en option pour les opérations de chiffrement et les clés

- Communication I2C jusqu’à 1 MHz

- Plage de fonctionnement : 3,3 V ±10 %, -40 °C à +125 °C

- Boîtier TDFN 3 mm x 4 mm à 10 broches

- AEC-Q100 classe 1

Applications

- Authentification automobile sécurisée

- Identification et étalonnage des pièces/outils/accessoires automobiles

- Protection cryptographique du nœud IoT

- Authentification sécurisée des accessoires et périphériques

- Stockage sécurisé des clés de chiffrement pour un contrôleur hôte

- Démarrage sécurisé ou téléchargement du micrologiciel et/ou des paramètres système

Vidéos

Schéma fonctionnel simplifié

Circuit d'application standard