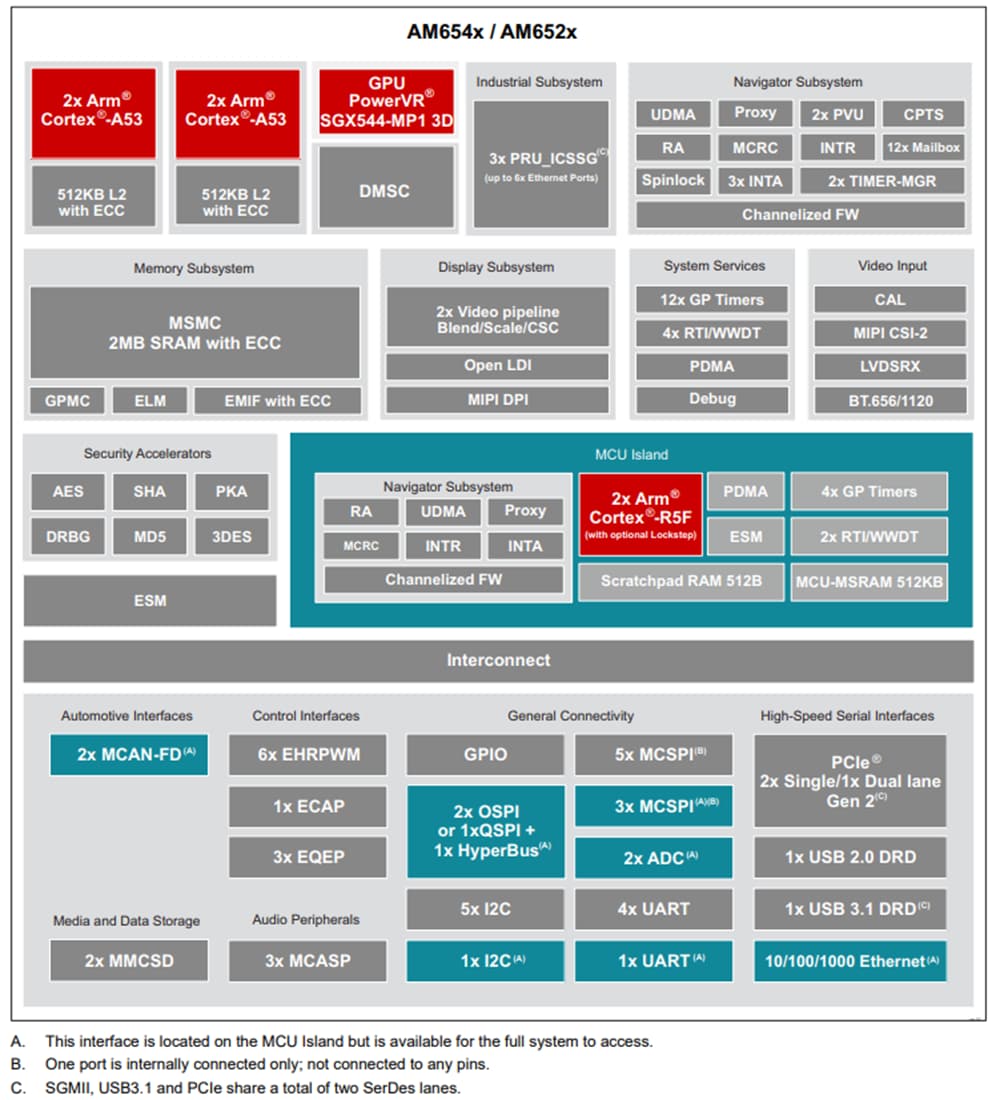

Texas Instruments Processeurs Arm™ AM654x/AM652x

Les processeurs Arm™AM654x/AM652x de Texas Instruments sont des processeurs d'application Arm® conçus pour répondre aux besoins complexes de traitement des produits intégrés modernes de l'industrie 4.0. Les dispositifs AM654x et AM652x combinent quatre ou deux cœurs Arm® Cortex®-A53 avec un double sous-système de microcontrôleurs Arm Cortex-R5F. Ces caractéristiques visent à aider les clients à atteindre les objectifs de sécurité fonctionnelle des produits finaux. Il comprend également trois sous-systèmes de communication industrielle Gigabit (PRU_ICSSG) pour créer un SoC capable de commandes industrielles haute performance avec une connectivité industrielle et un traitement pour les applications de sécurité fonctionnelle. L'AM65xx fait actuellement l'objet d'une évaluation en vue d'être certifié par TÜV SÜD conformément à la norme CEI 61508.Les quatre cœurs Arm Cortex-A53 dans l'AM654x sont disposés en deux groupes à double cœur avec une mémoire L2 partagée pour créer deux canaux de traitement. Les deux noyaux Arm Cortex-A53 de l'AM652x sont disponibles dans un groupe à double cœur unique et deux options de groupe à simple cœur. Une CCE étendue est incluse sur la mémoire sur puce, les périphériques et l’interconnexion pour plus de fiabilité. Le SoC, dans son ensemble, dispose de caractéristiques destinées à aider les clients à concevoir des systèmes capables d'atteindre des objectifs de sécurité fonctionnelle. L'accélération cryptographique et le démarrage sécurisé sont disponibles sur certains périphériques AM654x et AM652x en plus des pare-feu granulaires gérés par le DMSC.

Les processeurs RISC Arm Cortex-A53 fournissent une programmabilité avec une extension Arm Neon™. Le sous-système microcontrôleur (MCU) Arm Cortex-R5F double est disponible pour un usage général sous forme de deux cœurs, ou peut être utilisé en mode parallèle pour répondre aux besoins des applications de sécurité fonctionnelles. Les sous-systèmes PRU_ICSSG peuvent être utilisés pour fournir jusqu’à six ports Ethernet industriels tels que Profinet IRT, TSN, Ethernet/IP ou EtherCAT (entre autres), ou peuvent être utilisés pour la connectivité Gigabit Ethernet standard.

Texas Instruments fournit un ensemble complet d'outils logiciels et de développement pour les cœurs Arm, notamment un processeur SDK Linux, Linux-RT, RTOS, Android, des compilateurs C et une interface de débogage pour une visibilité de l'exécution du code source. La documentation sur la sécurité fonctionnelle applicable sera mise à disposition pour aider les clients à développer des systèmes de sécurité fonctionnelle ou liés à la sécurité.

Caractéristiques

- Cœurs de processeur

- Sous-système de microprocesseur Cortex-A53 double ou quadruple cœUR jusqu’à 1,1 GHz

- Jusqu’à deux faisceaux double cœur ou deux faisceaux mono-cœur Arm Cortex-A53 avec cache 512KB L2 incluant SECDED

- Chaque cœur A53 dispose d'un cache ICache L1 de 32 ko et DCache L1 de 32 K

- Cortex-R5F Arm double cœur jusqu'à 400 MHz

- Prend en charge le mode de verrouillage

- ICache 16 Ko, DCache 16 Ko et RAM 64 ko par cœur R5F

- Sous-système de microprocesseur Cortex-A53 double ou quadruple cœUR jusqu’à 1,1 GHz

- Sous-système industriel

- Trois sous-systèmes de communication industriels gigabit (PRU_ICSSG)

- Jusqu'à deux ports Ethernet 10/100/1000 par PRU_ICSSG

- Prend en charge deux ports SGMII

- Compatibilité avec PRU-ICSS 10/100 Mo

- 24 PWM par PRU_ICSSG

- Commande cycle par cycle

- Commande de déclenchement amélioré

- 18 filtres Sigma-delta par PRU_ICSSG

- Logique de court-circuit

- Logique de surintensité

- 6 interfaces d'encodeur de position multi-protocoles par PRU_ICSSG

- Trois sous-systèmes de communication industriels gigabit (PRU_ICSSG)

- Sous-système de mémoire

- Jusqu'à 2 Mo de RAM L3 sur puce avec SECDED

- Contrôleur de mémoire partagée multicœur (MSMC)

- SRAM jusqu'à 2Mo (2 bancs × 1Mo) avec SECDED

- SRAM partagée cohérente à mémoire mappée de niveau 2 ou de niveau 3

- Cache cohérent partagé de niveau 3

- Bus de port processeur 256 bits et bus d'adresse physique 40 bits

- Interfaces bidirectionnelles unifiées et cohérentes pour se connecter aux processeurs ou aux dispositifs maîtres

- Pré-échauffement et post-rinçage du cache L2, L3

- Gestion de la bande passante avec blocage limité

- Une interface principale d'infrastructure

- Interface principale de mémoire externe unique

- Prend en charge le système virtuel distribué

- Prend en charge le moteur DMA interne – Unité de routage de données (DRU)

- Protection contre les erreurs ECC

- SRAM jusqu'à 2Mo (2 bancs × 1Mo) avec SECDED

- Sous-système DDR (DDRSS)

- Prend en charge les types de mémoire DDR4 jusqu'à DDR-1600

- Bus de données 32 bits et bus SECDED 7 bits

- 8 Go d'espace adressable total

- Contrôleur de mémoire à usage général (GPMC)

- Composant semiconducteur SafeTI™

- Conçu pour les applications de sécurité fonctionnelle

- Développé conformément aux exigences de la norme CEI 61508

- Atteint l'intégrité systématique du SIL-3

- Pour l’îlot de sécurité du MCU, des diagnostics suffisants sont inclus pour atteindre les exigences d’intégrité des défauts aléatoires du SIL-2

- Pour le reste du SoC, des diagnostics suffisants sont inclus pour atteindre les exigences d'intégrité aléatoire des défaillances du SIL-2

- En outre, suffisamment de mesures architecturales sont en place pour permettre l'exécution des applications du SIL-3 avec un concept de sécurité approprié (par exemple, comparaison réciproque par logiciel)

- Manuel de sécurité fonctionnelle disponible

- Certification liée à la sécurité

- Certification de sécurité fonctionnelle au niveau des composants par TÜV SÜD [certification en cours]

- Caractéristiques de sécurité fonctionnelle

- ECC ou parité sur les mémoires critiques de calcul et l’interconnexion du bus interne

- Pare-feu permettant d'éviter les interférences (FFI)

- Auto-Test (BIST) intégré pour CPU, minuteurs haut de gamme et RAM sur puce

- Prise en charge de l’injection d’erreur matérielle pour le test de diagnostic

- Modules de signalisation des erreurs (ESM) pour la saisie des erreurs fonctionnelles liées à la sécurité

- Surveillance de la tension, de la température et de l'horloge

- Chronomètres de surveillance fenêtrés et non fenêtrés dans des domaines à multiples horloges

- Îlot MCU

- Isolation du sous-système de microprocesseur Arm Cortex-R5F à double cœur

- Tension, horloges, réinitialisations et périphériques dédiés séparés

- Connexion MCSPI interne au reste du SoC

- Sécurité

- Démarrage sécurisé pris en charge

- Racine de confiance appliquée par le matériel

- Prise en charge du basculement racine de confiance via la clé de sauvegarde

- Prise en charge de la protection contre les rachats, de la protection IP et de la protection contre les retournements

- Accélération cryptographique prise en charge

- Moteur cryptographique sensible aux sessions avec la possibilité de commuter automatiquement les matériaux clés en fonction du flux de données entrant

- Prend en charge les cœurs cryptographiques

- AES – tailles de clé 128/192/256 bits

- 3DES – tailles de clé 56/112/168 bits

- MD5, SHA1

- SHA2 – 224/256/384/512

- DRBG avec un véritable générateur de nombres aléatoires

- PKA (accélérateur de clé publique) pour aider au traitement RSA/ECC

- Prise en charge DMA

- Sécurité du débogage

- Accès sécurisé au débogage contrôlé par logiciel

- Débogage sensible à la sécurité

- Environnement d'exécution de confiance (TEE) pris en charge

- TEE basé sur Arm TrustZone

- Prise en charge étendue du pare-feu pour l'isolation

- Sécuriser le chemin DMA et l’interconnexion

- Sécuriser le chronomètre/minuteur/IPC

- Sécuriser la prise en charge de stockage

- Cryptage à la volée et prise en charge d'authentification pour l'interface OSPI

- Prise en charge de la sécurité réseau pour le cryptage/authentification des données (charge utile) via un moteur cryptographique matériel basé sur des paquets

- Coprocesseur de sécurité (DMSC) pour la gestion des clés et de la sécurité, avec un niveau de dispositif dédié, interconnexion pour le logiciel de sécurité

- Démarrage sécurisé pris en charge

- Services SoC

- Contrôleur de sécurité de gestion de périphérique (DMSC)

- Contrôleur de système SoC centralisé

- Gère les services système, y compris le démarrage initial, la sécurité, la sécurité fonctionnelle et la gestion horloge/réinitialisation/alimentation

- Contrôleur de gestion de l'alimentation pour les modes actif et basse consommation

- Communication avec les différentes unités de traitement sur le gestionnaire de messages

- Interface simplifiée pour optimiser les périphériques inutilisés

- Capacité de suivi et de débogage

- Seize minuteurs à usage général de 32 bits

- Deux sous-systèmes de navigation de contrôle et de mouvement de données (NAVSS)

- Accélérateur d'anneau (RA)

- DMA unifié (UDMA)

- Jusqu'à 2 gestionnaires de minuteurs (TM) (1024 minuteurs chacun)

- Contrôleur de sécurité de gestion de périphérique (DMSC)

- Multimédia

- Sous-système d'affichage

- Deux gestionnaires de superposition entièrement mappés en entrée associés à deux sorties d'affichage

- Interface parallèle DPI MIPI à un port

- Un port OLDI

- Unité de traitement graphique (GPU) 3D SGX544-MP1 PowerVR

- Une Interface série caméra-2 (MIPI CSI-2)

- Capture vidéo sur un port : BT.656/1120 (aucune synchronisation intégrée)

- Sous-système d'affichage

- Interfaces à haut débit

- Une interface Gigabit Ethernet (CPSW) prenant en charge

- RMII (10/100) ou RGMII (10/100/1000)

- IEEE1588 (2008 Annexe D, Annexe E, Annexe F) avec 802.1AS PTP

- Pontage audio/vidéo (P802.1Qav/D6.0)

- Ethernet économe en énergie (802.3 az)

- Cadres Jumbo (2024 octets)

- Clause 45 Gestion des MDIO PHY

- Deux sous-systèmes PCI-Express (PCIe) révision 3.1

- Prend en charge le fonctionnement Gen2 (5,0 GT/s)

- Deux lignes indépendantes ou un seul port à 2 voies

- Prise en charge du fonctionnement simultané du point de terminaison et complexe racine

- Sous-système de dispositif à double rôle (DRD) USB 3.1

- Un port Gen1 SuperSpeed amélioré

- Un port USB 2.0

- Chaque port est configurable indépendamment en tant qu'hôte USB, périphérique USB ou DRD USB

- Une interface Gigabit Ethernet (CPSW) prenant en charge

- Connectivité générale

- 6 ports de circuit inter-intégré (I2C™)

- Modules UART/IrDA/CIR configurables 5×

- Deux interfaces flash simultanées configurées comme

- Deux interfaces OSPI flash

- ou interface flash HyperBus™ et OSPI1

- Convertisseurs analogique-numérique (CAN) 2× 12 bits

- Jusqu'à 4 M d'échantillons/s

- Huit entrées analogiques multiplexées

- 8 Contrôleurs d'interfaces périphériques série multicanaux (MCSPI)

- Deux avec connexions internes

- Six avec interfaces externes

- Broches E/S à usage général (GPIO)

- Interfaces de commande

- 6 Modules de modulateurs d’impulsions à haute résolution améliorés (EHRPWM)

- Un module de saisie améliorée (ECAP)

- 3 Modules d’impulsions d’encodeur de quadrature amélioré (EQEP)

- Interfaces automobiles

- 2 modules de contrôleur de zone de réseau modulaire (MCAN) avec prise en charge CAN-FD complète

- Interfaces audio

- 3 Modules de port série audio multicanaux (MCASP)

- Média et stockage de données

- 2 interfaces (MMC™/ SD) numériques sécurisées / de Card™ multimédia

- Gestion simplifiée de l'alimentation

- Séquence d'alimentation simplifiée avec prise en charge complète des E/S à double tension

- Les LDO intégrés réduisent la complexité des solutions d'alimentation

- SDIO LDO intégré pour gérer la transition automatique de la tension pour l'interface SD

- Génération de réinitialisation à l'allumage (POR) intégrée réduisant la complexité de la solution d'alimentation

- Superviseur de tension intégré pour la surveillance de la sécurité fonctionnelle

- Détecteur de pannes d'alimentation intégré pour détecter les transitoires d'alimentation rapide

- Intégration analogique/système

- Détection intégrée de l'USB VBUS

- E/S à sécurité intégrée pour RÉINITIALISATION DDR

- Tous les pilotes de broches E/S sont désactivés pendant la réinitialisation pour éviter les conflits de bus

- Sorties E/S désactivées par défaut pendant la réinitialisation pour éviter les conflits système

- Prise en charge du changement de configuration pinmux E/S dynamique

- Architecture système sur puce (SoC)

- Prend en charge le démarrage principal à partir des interfaces UART, I2C, OSPI, HyperBus, NOR Flash parallèle, SD ou eMMC™, USB, PCIe et Ethernet.

- Technologie CMOS de 28 nm

- FCBGA (ACD) 784 broches 23 mm × 23 mm, pas de 0,8 mm

Applications

- Contrôleurs logiques programmables industriels (PLC)

- Automatisation industrielle avec fonctions de sécurité

- Communications multiprotocoles par bus de terrain

- Ordinateur industriel

- Robots industriels

- Interface homme-machine (IHM)

- Relais de protection d'infrastructure réseau

- Entraînements de moteurs robotiques

Vidéos

Schéma fonctionnel