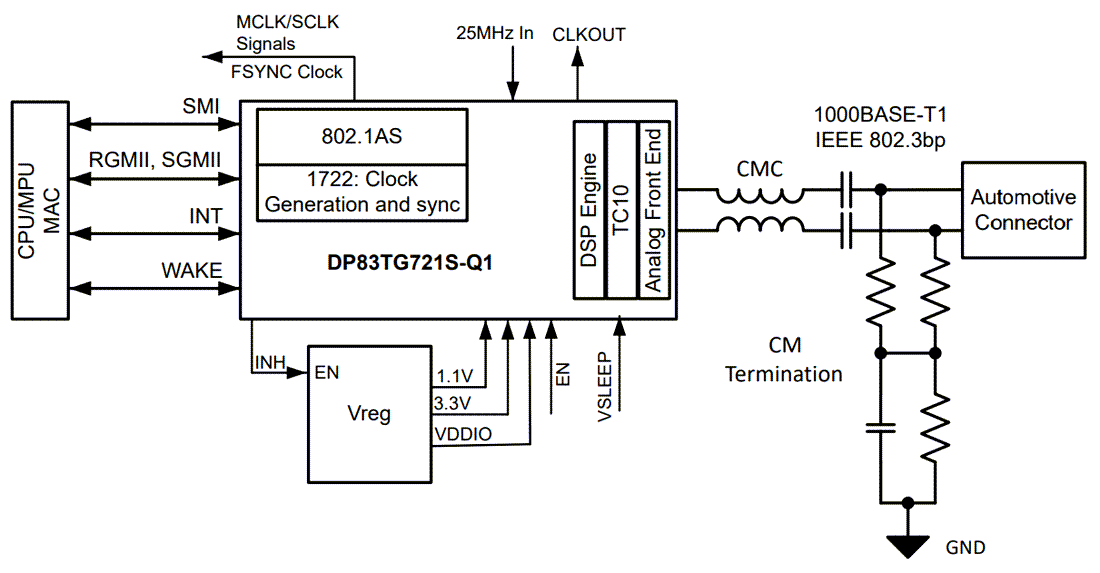

Texas Instruments Émetteur-récepteur PHY Ethernet DP83TG721-Q1 1000Base-T1

Texas Instruments DP83TG721-Q1 1000Base-T1 Ethernet PHY Transceiver is an IEEE 802.3bp and Open Alliance transceiver that provides all physical layer functions needed to receive and transmit data over unshielded/shielded single twisted-pair cables. The device offers xMII flexibility with support for RGMII and SGMII MAC interfaces. DP83TG721-Q1 supports the OA TC10 low-power sleep feature (with wake forwarding) to reduce system power consumption when communication is not required. This device offers the Diagnostic Tool Kit, with an extensive list of real-time monitoring tools, debug tools and test modes.Le DP83TG721-Q1 de Texas Instruments intègre l'horodatage matériel IEEE 1588v2/802.1AS et une PLL fractionnée, ce qui permet une synchronisation temporelle très précise. La PLL fractionnée permet une synchronisation fréquence/phase de l'horloge murale, ce qui élimine le besoin d'un VCXO externe en générant une large gamme fréquentielle à synchronisation temporelle nécessaires pour l'audio, pour la vidéo et pour d'autres applications d'ADAS. Le DP83TG721-Q1 intègre également le décodage IEEE 1722 CRF pour générer une horloge Media Clock (synchronisée avec l'horloge murale) pour l'AVB et pour d'autres normes audio. Le DP83TG721-Q1 peut également générer FSYNC/SCLK (synchronisation avec une horloge murale) pour l'interface I2S/TDM8 nécessaire aux applications audio.

Le DP83TG721-Q1 est compatible avec les PHY 100BASE-T1 et 1000BASE-T1 de TI, ce qui permet une évolutivité de conception à seule carte pour les deux vitesses.

Caractéristiques

- Conforme à la norme IEEE 802.3bp 1000BASE-T1

- Conformité OA TC10, moins de 20 µA de courant de veille

- Réveil local et distant et transfert de réveil

- TSN avancé

- Synchronisation temporelle IEEE 1588v2/802.1AS

- Horodatage matériel à correction intégrée de phase

- Signal très précis à 1 pps (±15 ns)

- Horloge audio

- Capacité de génération d'horloge de média AVB IEEE 1722

- Sortie d'horloge murale synchronisée en phase de 1 kHz à 50 MHz

- Génération d'horloge I2S et TDM8 SCLK/FSYNC/MCLK

- Interopérabilité Open Alliance TC12 et conformité à la norme EMC

- Conformité OA EMC

- Conforme CEM SAE J2962-3

- FPB intégré sur des broches MDI

- Interfaces MII, RMII, RGMII et Mac SGMII

- Tensions d'E/S prises en charge : 3,3 ; 2,5 ; et 1,8 V

- Compatibilité des broches avec les PHY 100BASE-T1 et 1000BASE-T1 de TI

- Conception de carte unique pour 100BASE-T1 et 1000BASE-T1 avec changement nécessaire de nomenclature

- Kit d'outils de diagnostic

- Suivi de la température, des tensions et des décharges électrostatiques (DES)

- Calculateur de débit de données avec générateur intégré de boîtiers MAC, compteur et vérificateur d'erreurs

- Indicateur de qualité des signaux

- Détection d'anomalies de câbles de type circuit ouvert ou court-circuit, basée sur la TDR

- CQI de surveillance de la dégradation de câbles

- Modes de boucle de retour

- Homologation AEC-Q100

- DES IEC61000-4-2 (décharge de contact à ±8 kV)

Applications

- Unité de contrôle télématique (TCU, TBOX)

- AVB

- ADAS (LiDAR, RADAR, caméra frontale)

- Commande de zone, de passerelle et de carrosserie

Ressources supplémentaires

Schéma simplifié