Texas Instruments Pont PCI vers PCI PCI2050B

Le pont PCI vers PCI PCI2050B de Texas Instruments dispose d'un chemin de connexion à hautes performances entre deux bus d'interconnexion de composants périphériques (PCI) fonctionnant à une fréquence maximale de bus de 66 MHz. Les transactions se produisent entre des maîtres sur un et des cibles sur un autre bus PCI. Le pont PCI2050B permet aux transactions pontées de se produire simultanément sur les deux bus. Le pont PCI-vers-PCI prend en charge les transferts en mode rafale pour maximiser le débit de données, et les deux chemins de trafic du bus à travers le pont agissent indépendamment.Le pont PCI2050B de TI est conforme à la caractéristique technique du bus local PCI et est utilisé pour surmonter les limites de charge électrique de 10 dispositifs par bus PCI et un dispositif PCI par port d’extension en créant des bus hiérarchiques. Le PCI2050B fournit un arbitrage interne à deux niveaux jusqu'à neuf maîtres de bus secondaire et peut être mis en œuvre avec un arbitre de bus externe.

La fonction PCI étendue d’échange à chaud de CompactPCI™ fait du pont PCI2050B une solution idéale pour les cartes PCI compactes multifonctions et l’adaptation des cartes à fonction unique à la conformité d’échange à chaud.

Caractéristiques

- Deux bus PCI 32 bits, 66 MHz

- Logique de cœur 3,3 V avec interfaces PCI universelles compatible avec les environnements de signalisation PCI 3,3 V et 5 V

- Arbitrage interne à deux niveaux jusqu'à neuf maîtres de bus secondaire et prend en charge un arbitre de bus secondaire externe

- Dix sorties d'horloge PCI secondaires

- Tampons de lecture et d'écriture indépendants pour chaque direction

- Transfert de données en rafale avec une architecture de pipeline pour maximiser le débit de données dans les deux sens

- Prend en charge l'écriture combinée pour un débit de données amélioré

- Prend en charge le délai cadre-à-cadre de seulement quatre horloges PCI d'un bus à l'autre

- Jusqu'à trois transactions retardées dans les deux directions

- Propagation de verrouillage de Bus

- Latence prévisible selon la caractéristique technique du bus local PCI

- Architecture configurable pour caractéristique technique d'interface de gestion de l'alimentation du bus PCI

- Fonctionnalité de remplacement à chaud CompactPCI

- Le bus secondaire est abaissé pendant la réinitialisation

- Options de décodage d'E/S et de mémoire VGA/palette

- Technologie CMOS à faible puissance et sous-micron avancée

- Boîtier BGA™ MicroStar PDV 208 bornes, PPM 208 bornes ou 257 bornes

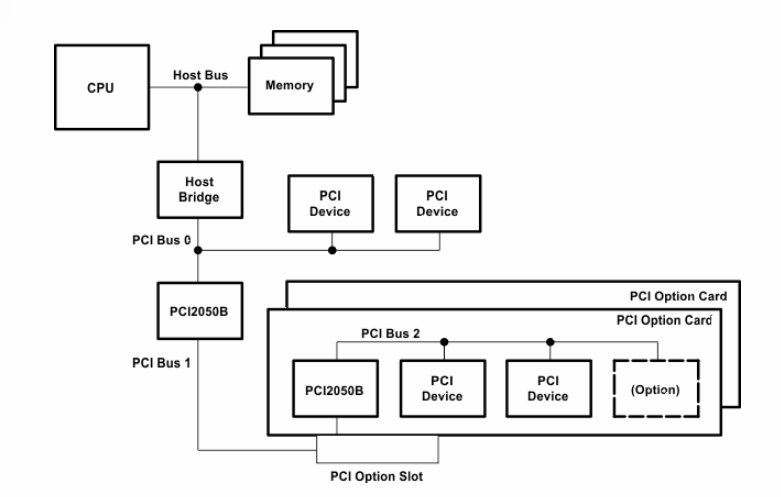

Schéma fonctionnel

Publié le: 2021-02-03

| Mis à jour le: 2022-03-11