Texas Instruments Registres de décalage SIPO SN74AC596/SN74AC596-Q1

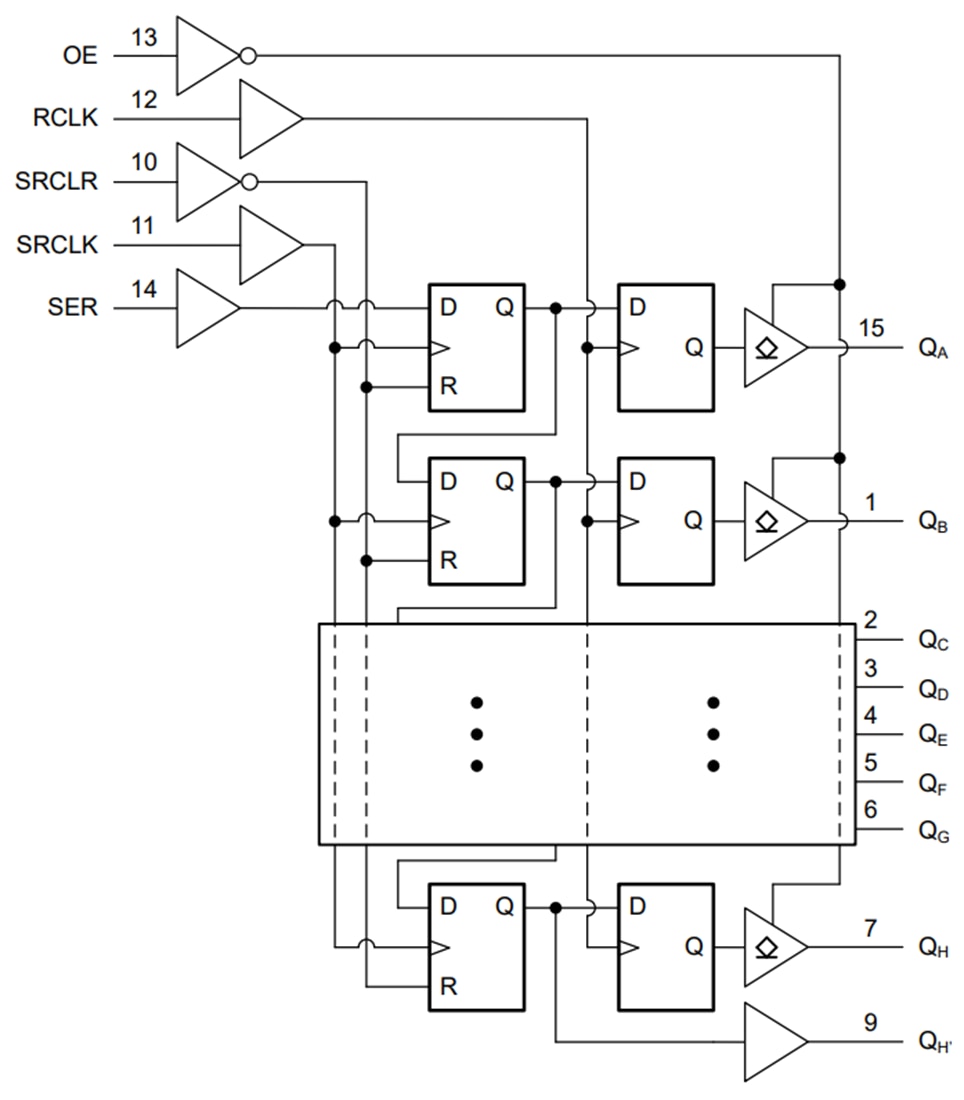

Les registres de décalage SIPO SN74AC596/SN74AC596-Q1 de Texas Instruments contiennent un registre de décalage série-parallèle (SIPO) de 8 bits qui alimente un registre de stockage de type D de 8 bits. Le registre de stockage a des sorties parallèles à drain ouvert. Des horloges distinctes sont fournies pour le registre de stockage et le registre de décalage. Le registre à décalage possède une entrée série (SER), une entrée de remplacement direct transparent (SRCLR\) et un sortie série (QH') pour la mise en cascade. Lorsque l'entrée d'activation de sortie (OE) est élevée, les sorties sont en état d'impédance élevée. Les données du registre interne ne sont pas affectées par l'exploitation de l'entrée OE\. Les dispositifs SN74AC596-Q1 de Texas Instruments sont qualifiés AEC-Q100 pour les applications automobiles.Caractéristiques

- Plage de fonctionnement large de 1,5 V à 6 V

- Les entrées acceptent des tensions jusqu'à 6 V

- Sortie continue ±24 mA à 5 V

- Prend en charge une commande de sortie allant jusqu'à ±75 mA à 5 Ven courtes rafales

- Moteurs lignes de transmission 50 Ω

- tpd maximum de 11,4 ns à 5 V, charge de 50 pF

Applications

- Augmenter le nombre de sorties sur un microcontrôleur

- Stocker temporairement jusqu'à 8 bits de données

Ressources supplémentaires

- Fiche technique SN74AC596

- Fiche technique SN74AC596-Q1

- Note d'application - Implications des entrées CMOS lentes ou flottantes

- Guide de sélection : guide logique

- Note d'application — Comprendre et interpréter les fiches techniques de logique standard

- Guide d'utilisation : Livre de données de poche logique

- Note d'application : Conception avec logique

- Note d'application : Utilisation de la technologie CMOS haute vitesse et de la technologie CMOS avancée dans les systèmes avec plusieurs VCC

- Systèmes d'aide à la conduite automobile (système d'aide à la conduite (ADAS))

Schéma fonctionnel

Publié le: 2025-03-25

| Mis à jour le: 2025-05-06