NXP Semiconductors LPC546xx 32-bit Cortex-M4 MCUs

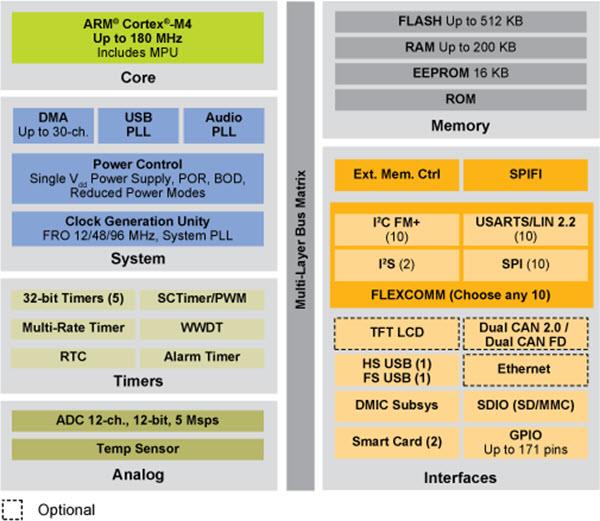

NXP Semiconductors LPC546xx 32-bit Microcontrollers (MCUs) offer a rich peripheral set with very low power consumption and enhanced debug features. The LPC546xx MCU family, powered by the Arm® Cortex®-M4 core, offers Ethernet support, a TFT LCD controller, and two CAN FD modules. Designed for flexibility and performance scalability, LPC546xx MCUs provide up to 180MHz performance while retaining power-efficiency as low as 120uA/MHz. With up to 21 communication interfaces, LPC546xx MCUs are ideal for the HMI and connectivity needs of next-generation IoT applications. NXP LPC546xx 32-bit Microcontrollers are offered in TFBGA180 and LQFP208 packagesFeatures

- Arm Cortex-M4 core running at a frequency of up to 180MHz

- On-chip memory:

- Up to 512KB on-chip flash program memory with flash accelerator and 256-byte page erase and write

- Up to 200KB total SRAM consisting of 160KB contiguous main SRAM and an additional 32KB SRAM on the I&D buses. 8KB of SRAM bank

- intended for USB traffic

- 16KB of EEPROM

- ROM API support

- Multiple USART, SPI, and I2C serial interfaces

- Two ISO 7816 Smart Card Interfaces with DMA support

- USB 2.0 high-speed host/device controllers

- USB 2.0 full-speed host/device controller with on-chip PHY and dedicated DMA controller supporting crystal-less operation in device mode

- SPIFI with XIP feature uses up to four data lines to access off-chip SPI/DSPI/QSPI flash memory at a much higher rate than standard SPI or SSP interfaces

- Ethernet MAC with MII/RMII interface with Audio Video Bridging (AVB) support and dedicated DMA controller

- Two CAN FD modules with a dedicated DMA controller

- Multiple digital peripherals including 30 channel DMA controller, LCD controller, external memory controller

- Secured digital input/output (SD/MMC and SDIO) card interface with DMA support

- Five 32-bit general-purpose timers/counters

- 32-bit Real-time clock (RTC)

- Windowed Watchdog Timer (WWDT)

- Repetitive Interrupt Timer (RIT) for debug time stamping and for general purpose use

- Programmable PMU (Power Management Unit) to minimize power consumption and to match requirements at different performance levels

- Reduced power modes: sleep, deep-sleep, and deep power-down

- Wake-up from deep-sleep modes due to activity on the USART, SPI, and I2C peripherals when operating as slaves

- Available in TFBGA180 and LQFP208 packages

Videos

Block Diagram

Additional Resources

View Results ( 24 ) Page

| Numéro de pièce | Package/Boîte | Taille de la mémoire du programme | Taille de la RAM de données | Fiche technique |

|---|---|---|---|---|

| LPC54618J512BD208E | LQFP-208 | 512 kB | 200 kB |  |

| LPC54606J256ET100E | TFBGA-100 | 256 kB | 136 kB |  |

| LPC54606J512BD208K | 512 kB | 200 kB |  |

|

| LPC54605J512ET180K | 512 kB | 200 kB |  |

|

| LPC54607J256BD208E | LQFP-208 | 256 kB | 136 kB |  |

| LPC54605J256BD100E | LQFP-100 | 256 kB | 136 kB |  |

| LPC54616J256ET180E | TFBGA-180 | 256 kB | 136 kB |  |

| LPC54605J256ET180E | TFBGA-180 | 256 kB | 136 kB |  |

| LPC54605J512ET100E | TFBGA-100 | 512 kB | 200 kB |  |

| LPC54606J512BD100E | LQFP-100 | 512 kB | 200 kB |  |

Publié le: 2017-02-16

| Mis à jour le: 2022-03-11